3.2 Counter

Counter (pencacah) merupakan rangkaian yang berfungsi menghitung atau mencacah banyaknya pulsa clock dan sebagai pembagi frekuensi, pembangkit kode biner dan grey. Menurut macamnya, terdapat counter yang dapat dicacah dan pencacah modulo. Seperti contoh, modulo-2, modulo-4, modulo-5 dan masih banyak lagi. Apabila clock dimulai dari 0, maka pada modulo-2 terdapat dua bilangan yang dicacah, yaitu dari 0 ke 1. Terdapat dua jenis counter yaitu asynchronous counter dan synchronous counter

Pencacah tak sinkron (asyncronous counter) merupakan pencacah yang memiliki flip-flop bergulingan secara tak serempak, tetapi berurutan. Karena hanya flip-flop yang paling ujung saja yang dikendalikan oleh sinyal clock, untuk flip-flop lainnya dikendalikan dari masing-masing flip-flop sebelumnya. Banyaknya denyut dimasukkan dan diterjemahkan oleh flip-flop ke dalam bentuk biner. Karena itulah pencacah tak sinkron juga disebut pencacah biner. Pada pencacah tak sinkron terdapat beberapa jenis yaitu sebagai berikut:

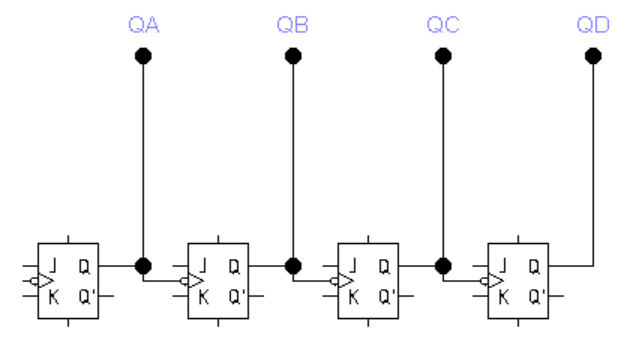

Counter ini dapat menghitung bilangan biner dengan urutan dari bawah ke atas. Apabila digunakan 4 buah flip-flop, maka kita dapat melakukan hitungan paling tinggi adalah 1111. Counter yang dapat menghitung sampai 1111 disebut 4 bit binary counter. Oleh karena itu dapat menghitung dengan cara ke atas, maa di sebut pula asynchronous 4 binary up counter. Rangkaian berikut ini adalah pencacah maju tak sinkron yang menggunakan 4 buah JK-FF.

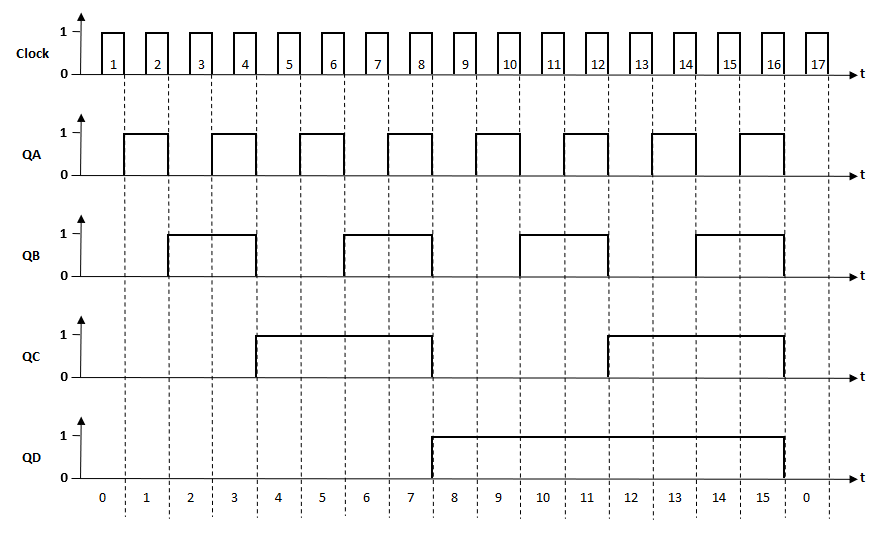

Pada gambar 23 rangkaian pencacah tak sinkron maju input J dan K dari seluruh flip-flop dibuat dalam keadaan 1. Sebelum pulsa pertama yang akan dihitung masuk ke input, maka seluruh output counter QA, QB, QC dan QD dibuat 0 terlebih dahulu dengan jalan membuat clear dalam keadaan 0 walaupun sesaat. Diagram perwaktuan untuk rangkaian di atas adalah sebagai berikut:

Karena masing-masing flip-flop berfungsi sebagai pembagi dua, maka frekuensi masing-masing outputnya adalah sebagai berikut:

QA $= \frac{1}{2}$ frekuensi sinyal clock.

QB $= \frac{1}{2}$ frekuensi QA $= \frac{1}{4}$ frekuensi sinyal clock.

QC $= \frac{1}{2}$ frekuensi QB $= \frac{1}{8}$ frekuensi sinyal clock.

QD $= \frac{1}{2}$ frekuensi QC $= \frac{1}{16}$ frekuensi sinyal clock.

Tabel kebenaran untuk rangkaian pencacah tak sinkron maju adalah sebagai berikut:

| $Clock$ | $QD$ | $QC$ | $QB$ | $QA$ | $Desimal$ |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 0 | 1 | 1 |

| 3 | 0 | 0 | 1 | 0 | 2 |

| 4 | 0 | 0 | 1 | 1 | 3 |

| 5 | 0 | 1 | 0 | 0 | 4 |

| 6 | 0 | 1 | 0 | 1 | 5 |

| 7 | 0 | 1 | 1 | 0 | 6 |

| 8 | 0 | 1 | 1 | 1 | 7 |

| 9 | 1 | 0 | 0 | 0 | 8 |

| 10 | 1 | 0 | 0 | 1 | 9 |

| 11 | 1 | 0 | 1 | 0 | 10 |

| 12 | 1 | 0 | 1 | 1 | 11 |

| 13 | 1 | 1 | 0 | 0 | 12 |

| 14 | 1 | 1 | 0 | 1 | 13 |

| 15 | 1 | 1 | 1 | 0 | 14 |

| 16 | 1 | 1 | 1 | 1 | 15 |

Pencacah dapat mencacah dari bilangan biner 0000 sampai dengan 1111 (dari 0 sampai 15 desimal).

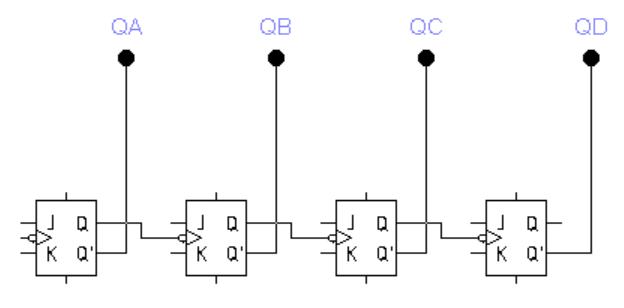

Prinsip kerja dari counter ini adalah kebalikan dari up counter, yaitu menghitung bilangan biner dengan urutan mulai dari atas ke bawah (dari besar ke kecil). Prinsip kerjanya pun tidak jauh beda dari up counter. Bedanya hanya setiap output flip-flop diambil dari output $\bar{Q}$, sedangkan input clocknya dihubungkan dengan output Q dari flip-flop sebelumnya. Perhatikan rangkaian berikut untuk lebih jelasnya.

Pada gambar 25 adalah rangkaian pencacah tak sinkron mundur, prinsip kerja dari rangkaian tersebut yaitu sebelum pulsa pertama datang dan masuk ke input, seluruh output counter QA, QB, QC, dan QD dibuat 0 dengan menggunakan direct clear walaupun sebentar saja. Pada saat pulsa pertama bergerak dari 1 ke 0, maka output flip-flop 0 akan berubah menjadi 1. $\bar{Q}$ flip-flop A berubah menjadi 1 ke 0 juga. Hasil perubahan ini akan masuk ke flip-flop 1 sehingga menyebabkan output QB menjadi 1. Hal yang sama juga terjadi pada flip-flop QB dan QC sehingga output mereka berubah menjadi 1. Jadi sesudah pulsa pertama masuk output counter berubah menjadi 1111.

Pencacah sinkron (synchronous counter) disebut juga pencacah jajar. Input untuk denyut-denyut lonceng/clock dikendalikan secara serempak. Dengan demikian penundaan pencacah adalah sama dengan penundaan flip-flop. Pencacah sinkron memerlukan sirkuit loncang/clock yang berdaya tinggi, sebab lonceng harus menggerakkan semua flip-flop.

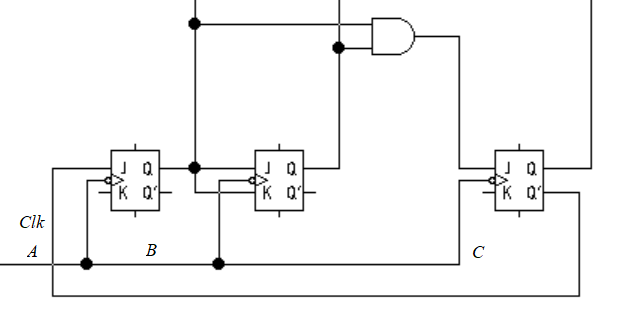

Pencacah sinkron maju (up counter) melakukan pengitungan dari bawah ke atas. Pada counter ini pulsa yang ingin dihitung masuk ke dalam setiap flip-flop secara serentak (bersama-sama) sehingga perubahan output setiap flip-flop akan terjadi secara serentak. Berikut adalah contoh rangkaian untuk pencacah sinkron maju.

Dapat dilihat pada gambar 26, saluran Clk setiap flip-flop akan dihubungkan dalam sebuah sambungan agar clock pulsa bisa dijalankan bersamaan. Flip-flop yang paling depan berfungsi sebagai LSB dengan saluran J dan K diberikan data bit sebesar 1 secara tetap. Sementara itu, saluran J dan K pada flip-flop yang lain dikendalikan berdasarkan kombinasi keluaratan flip-flop sebelumnya. Tabel kebenaran untuk rangkaian pencacah sinkron maju adalah sebagai berikut:

| $Clock$ | $Output$ | $FFC$ | $FFB$ | $FFA$ | |||||

|---|---|---|---|---|---|---|---|---|---|

| $C$ | $B$ | $A$ | $JC$ | $KC$ | $JB$ | $KB$ | $JA$ | $KA$ | |

| 0 | 0 | 0 | 0 | 0 | $x$ | 0 | $x$ | 1 | $x$ |

| 1 | 0 | 0 | 1 | 0 | $x$ | 1 | $x$ | $x$ | 1 |

| 2 | 0 | 1 | 0 | 0 | $x$ | $x$ | 0 | 1 | $x$ |

| 3 | 0 | 1 | 1 | 1 | $x$ | $x$ | 1 | $x$ | 1 |

| 4 | 1 | 0 | 0 | $x$ | 1 | 0 | $x$ | 0 | $x$ |

| 5 | 1 | 0 | 1 | $x$ | $x$ | $x$ | $x$ | $x$ | $x$ |

| 6 | 1 | 1 | 0 | $x$ | $x$ | $x$ | $x$ | $x$ | $x$ |

| 7 | 1 | 1 | 1 | $x$ | $x$ | $x$ | $x$ | $x$ | $x$ |

FFC merupakan flip-flop JK C. Terdapat tiga flip-flop JK pada rangkaian pencacah sinkron maju. JC dan KC adalah masing-masing input pada gerbang JK C. Karena merupakan modulo-5, maka pada urutan clock ke-5, angka kembali ke 0000.

Pencacah sinkron mundur (down counter) melakukan penghitungan dari atas ke bawah .Sama seperti pencacah sinkron maju, FFC merupakan flip-flop JK C. Terdapat tiga flip-flop JK pada rangkaian. JC dan JK adalah masing-masing input pada gerbang JK C. Karena merupakan modulo-5, maka pada urutan clock ke-5 angka kembali pada 000.

Agar lebih memahami mengenai rangkaian counter silakan klik selanjutnya