3.1 Flip-Flop

Flip-flop merupakan komponen yang dianggap cukup penting dalam memori. Cara kerja sebuah flip-flop adalah mengubah keluaran yang awalnya tidak dapat untuk menyimpan suatu data menjadi keluaran yang dapat digunakan untuk menyimpan data. Jenis-jenis flip-flop adalah sebagai berikut.

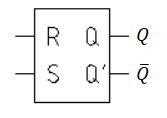

Flip-flop RS merupakan jenis flip-flop yang paling sederhana. Nama lain dari RS flip-flop adalah Set-Clear Flip-flop (SC-FF). Dalam flip-flop RS terdapat dua masukan, yaitu R (Reset) merupakan masukan yang digunakan untuk membuat output mempunyai kondisi 0 dan S (Set) digunakan untuk membuat output mempunyai kondisi 1. Adapun simbol RS flip-flop sebagai berikut:

Flip-flop RS dapat diimplementasikan dari beberapa jenis gerbang, yaitu sebagai berikut.

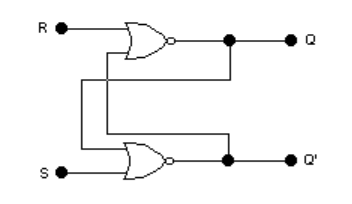

Rangkaian flip-flop dalam gerbang NOR adalah sebagai berikut.

Dapat dilihat rangkaian flip-flop gerbang NOR pada gambar 18, bahwa output dari gerbang R dioper ke gerbang S dan sebaliknya, dari gerbang S dioper ke gerbang R. Pada gerbang NOR, input yang mempunyai nilai 1 pada S akan mempunyai output nilai 1 (seperti pada fungsi set) dan input yang mempunyai nilai 1 pada R akan mempunyai output nilai 0 (seperti pada fungsi reset). Apabila kedua input bernilai 0, maka output akan tetap pada nilai terakhirnya. Untuk input yang keduanya bernilai 1, maka outputnya terlarang atau harus dihindari.

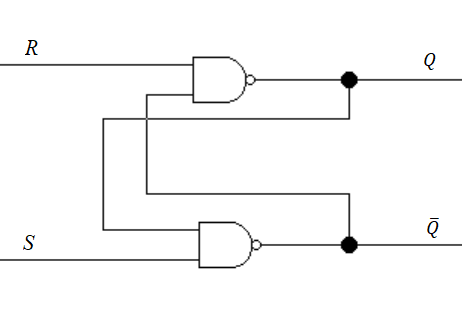

Rangkaian flip-flop dalam gerbang NAND adalah sebagai berikut:

Rangkaian flip-flop dalam gerbang NAND pada gambar 19, prinsip kerjanya sama persis dengan rangkaian flip-flop gerbang NOR. Karena flip-flop bekerja berdasarkan prinsip RS, yaitu reset dan set.

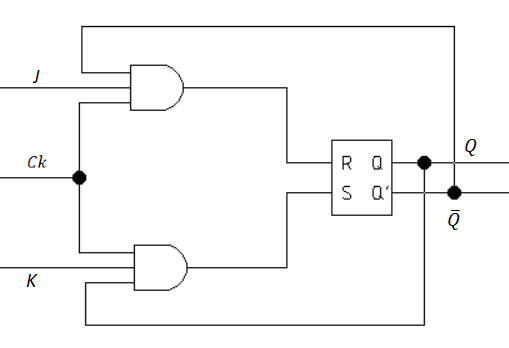

Flip-flop jenis ini merupakan penyempurnaan flip-flop RS. Pada flip-flop RS, saat kedua input bernilai 1, maka hasilnya harus dihindari, Flip-flop JK mempunyai dua input, yaitu J dan K. Perhatikan gambar rangkaian flip-flop JK berikut ini:

Pada gambar 20, saat input J dan K masing-masing adalah 0, Q tetap pada nilai terakhirnya. Pada saat J rendah dan K tinggi, gerbang atas tertutup, maka tidak terdapat kemungkinan untuk mengeset flip-flop. Pada saat Q tinggi, gerbang bawah melewatkan pemicu reset segera setelah pinggiran pulsa clock positif berikutnya tiba. Hal ini membuat Q menjadi rendah. Oleh karena itu J = 0 dan K = 1 yang berarti bahwa pinggiran pulsa clock positif, dan selanjutnya akan mereset flip-flopnya. Pada saat J tinggi dan K rendah, gerbang bawah tertutup. Pada saat J dan K keduanya tinggi, dapat mengeset atau mereset flip-flopnya. Tabel kebenaran untuk rangkaian flip-flop JK FF adalah sebagai berikut.

| `Input` | `Output` | ||

|---|---|---|---|

| `Clock` | `J` | `K` | `Q` |

| 0 | 0 | Nilai Terakhir | |

| 1 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 1 | Dilarang | |

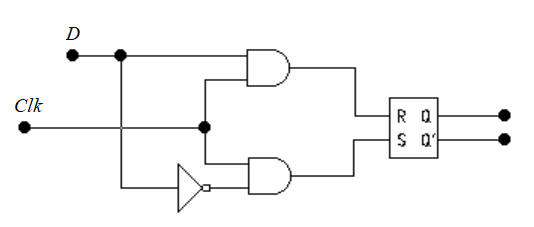

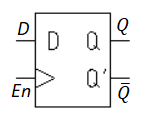

Flip-flop D merupakan flip-flop yang berasal dari kata delay. Flip-flop D hanya mempunyai satu jenis masukan. Flip-flop ini hanya mempunyai satu jenis nilai masukan. Jenis flip-flop ini mencegah nilai D mencapai output Q sampai berlangsungnya clock. Perhatikan rangkaian flip-flop D berikut ini:

Cara kerja rangkaian flip-flop D pada gambar 21 ini adalah apabila clock rendah, kedua gerbang AND tertutup, maka D dapat berubah nilai tanpa memengaruhi nilai Q. Sebaliknya, bila clock tinggi, kedua gerbang AND terbuka. Hal ini menyebabkan, Q terdorong untuk menyamai nilai D. Bila clock turun kembali, Q tidak berubah dan menyimpan nilai D yang terakhir. Berikut ini simbol dari rangkaian D FF.

Agar lebih memahami mengenai rangkaian flip-flop silakan klik selanjutnya